# FPGA-Based Design and Implementation of Spread-Spectrum Schemes for Conducted-Noise Reduction in DC-DC Converters

Gamal M. Dousoky<sup>1</sup> Masahito Shoyama<sup>1</sup> Tamotsu Ninomiya<sup>2</sup>

Kyushu University, 744 2-626-1 motooka, nishi-ku, Fukuoka, 819-0395 Japan

Nagasaki University, 1-14 Bunkyo-machi, Nagasaki, 852-8521 Japan E-mail: dousoky@ieee.org

*Abstract-* In this paper many spread-spectrum schemes, several of which are new, have been designed and implemented for conducted-noise reduction in DC-DC converters. A field-programmable gate array (FPGA) has made substantial improvements in price and performance throughout the past few years. The implementation of the schemes has been accomplished by using FPGA-based controller.

A breadboard circuit has been built-up for investigating the effect of all the proposed schemes on conducted-noise spectrum in DC-DC converters. Furthermore, a comparative study has been carried-out to reach the most efficient scheme in spreading the conducted-noise spectrum.

Experimental results show that randomizing each of carrier frequency, duty-ratio, and the pulse position parameters significantly improves the conducted-noise spectrum and effectively reduces the noise peaks at both high and low frequency ranges.

## I. INTRODUCTION

DC-DC converters are important in portable electronic devices such as cellular phones , laptop computers, and electric vehicles, which are supplied with power from a DC power source such as batteries, photovoltaic cells, or fuel cells. Such electronic devices often contain several sub-circuits, with each sub-circuit requiring a unique voltage level different from that supplied by the source, [1] - [3].

Switching power converters have been reported to generate common-mode and differential-mode conducted-noise in addition to radiated-noise. They may cause serious problems by generating such switching noise. Although switching converters produce significant amounts of switching noise, they are also required to operate inside electromagnetic interference (EMI) sensitive applications, [4] and [5]. This research aims to reduce the switching noise produced by DC-DC converters.

Traditional tools for EMI suppression are related to the use of filters and shielding techniques. But these tools are bulky and require expensive passive components, which makes them unsuitable for space-limited and price-sensitive portable devices, [5] and [6]. Alternative, pre-emptive EMI mitigation techniques eliminate the need for EMI filters by spreading the switching converters noise over a frequency range, [7]–[14]. By using these techniques, the noise generated by the Switching-Mode Power Supplies (SMPS) can be spread across a well defined frequency band. As a result, the average spectral power density of the broadband noise can thus be drastically reduced, [15].

FPGA is an attractive hardware design option. It has made substantial improvements in price and performance throughout the past few years, [16]. For an excellent overview of the classical and recent developments in FPGA technology. focusing on industrial control system applications, the reader is referred to [17]. Although FPGA implementation is now widespread in a range of military, defense, and signal processing applications, it is much flexible than analog control, becoming lower cost, and applicable for power supply applications. The implementation of the spread-spectrum schemes has been accomplished by using FPGA-based digital controller.

The paper is organized as follows: Section II presents spread-spectrum schemes in DC-DC converters. The design and implementation of the proposed FPGA-based controller which includes pseudorandom streams generator and digital pulse-width modulator are addressed in section III. Section IV describes the details of the experimental test circuit. Experimental results and discussion are presented in section V. Finally, conclusions and future work have been presented in section VI.

#### II. SPREAD-SPECTRUM SCHEMES IN DC-DC CONVERTERS

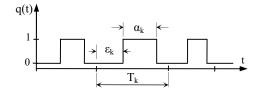

According to Fig. 1,  $T_k$  is the duration of the k<sup>th</sup> cycle,  $\alpha_k$  is the duration of the on-state within this cycle, and  $\varepsilon_k$  is the delay from the starting of the switching cycle to the turn-on within the cycle. Note that the duty ratio is  $d_k = \alpha_k / T_k$  and the switching frequency  $F_k=1/T_k$ .

Fig. 1. Randomization parameters in the switching signal.

The switching function q(t) consists of a series of such switching cycles. In order to spread the frequency spectrum of the switching noise, {F<sub>k</sub>, d<sub>k</sub>, or  $\varepsilon_k$ } can be randomized. Table I summarizes all the possible schemes that can be carried-out for this purpose.

Some randomization schemes used in power electronics are, [7] - [14]:

- Randomized pulse position modulation (RPPM):

ε<sub>k</sub> changes; F<sub>k</sub>, and d<sub>k</sub> are fixed;

- Randomized pulse width modulation (RPWM): d<sub>k</sub> changes; F<sub>k</sub>, and ε<sub>k</sub> are fixed;

- Randomized carrier frequency modulation with fixed duty ratio (RCFMFD): F<sub>k</sub>, changes; d<sub>k</sub>, and ε<sub>k</sub> are fixed;

- Randomized carrier frequency modulation with variable duty ratio (RCFMVD): F<sub>k</sub>, and d<sub>k</sub> change; ε<sub>k</sub> is fixed.

On the other hand, as in Table I, still another three different randomization schemes which haven't been addressed before; due to hardware limitations and the complexity of the control circuit. These schemes are:

- Randomized duty ratio, randomized pulse position modulation with fixed carrier frequency (RDRPPMFCF): d<sub>k</sub>, and ε<sub>k</sub> change; F<sub>k</sub> is fixed;

- Randomized carrier frequency, randomized pulse position modulation with fixed duty ratio (RCFRPPMFD): F<sub>k</sub>, and ε<sub>k</sub> change; d<sub>k</sub> is fixed;

- Randomized carrier frequency, randomized duty ratio, with randomized pulse position modulation (RRRM): F<sub>k</sub>, d<sub>k</sub>, and ε<sub>k</sub> change.

TABLE I

THE RANDOMIZATION PARAMETERS FOR THE SCHEMES.

| 1    |           | Dendensiertien Demonsterre |        |        |               |         |

|------|-----------|----------------------------|--------|--------|---------------|---------|

| Case | Scheme    | Randomization Parameters   |        |        | $\alpha_k$    | Remarks |

|      |           | $\mathbf{F}_{\mathbf{k}}$  | $d_k$  | ε      | ₩K.           |         |

| (a)  | PWM       | Const.                     | Const. | Const. | Const.        | Basic   |

| (b)  | RPPM      | Const.                     | Const. | Rand.  | Const.        | Ad.*    |

| (c)  | RPWM      | Const.                     | Rand.  | Const. | Rand.         | Ad.*    |

| (d)  | RDRPPMFCF | Const.                     | Rand.  | Rand.  | Rand.         | New     |

| (e)  | RCFMFD    | Rand.                      | Const. | Const. | Rand.; Synch. | Ad.*    |

| (f)  | RCFRPPMFD | Rand.                      | Const. | Rand.  | Rand.; Synch. | New     |

| (g)  | RCFMVD    | Rand.                      | Rand.  | Const. | Rand.         | Ad.*    |

| (h)  | RRRM      | Rand.                      | Rand.  | Rand.  | Rand.         | New     |

Ad.\*: Addressed before in power electronics publications.

Now, with the flexibility and programmability of the FPGA technology, the above new schemes have been designed, implemented and addressed in this paper. Moreover, the other schemes, used before in power electronics, have been designed and implemented as well. Furthermore, all schemes have been experimentally investigated and conducted-noise spectrums have been compared in the following sections.

#### III. DESIGN AND IMPLEMENTATION OF THE PROPOSED FPGA-BASED CONTROLLER

This section presents the design and implementation of the proposed FPGA-based controller which includes pseudorandom stream generator and digital pulse-width modulator.

## A. Pseudorandom Streams Generator

As discussed in the previous section, in order to spread the noise spectrum,  $\{F_k, d_k, \text{ or } \epsilon_k\}$  can be randomized. Hence three random number generators are needed to realize all the addressed schemes.

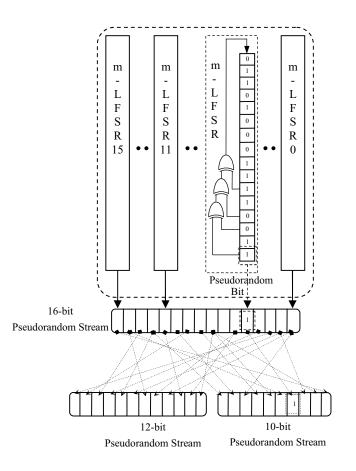

Fig. 2. The proposed pseudorandom streams generator.

A pseudorandom streams generator has been constructed for this purpose. As shown in Fig. 2, the proposed construction uses several maximum length linear feedback shift registers (m-LFSRs) in parallel. The use of m-LFSRs is due to the fact that the sequence generated by the m-LFSRs has a maximum period. For different m-LFSRs output bits, different initial contents of m-LFSRs (seeds) have been used. The taps are XOR'd sequentially with the output and then fed back into the leftmost bit.

The designed pseudorandom streams generator delivers three different random streams; (16-bit, 12-bit, and 10-bit streams). The 16-bit stream is composed of the output bits of the m-LFSRs. Furthermore, the 12-bit and 10-bit streams are composed of some of these bits with different arrangements. The m-LFSRs are clocked regularly; i.e., the movement of the data in all the m-LFSRs is controlled by the same clock.

Only at the beginning of every switching cycle, the random output bits are converted into an integer numbers (RFS, RDS, and RES) and used in the digital pulse-width modulator (DPWM). However, the other generated random output bits are discarded.

## B. Digital Pulse-Width Modulator

At the beginning of every switching cycle, the DPWM achieves the following assignments:

- 1. Converting the pseudorandom (16-bit, 10-bit and 12bit) streams into integer numbers (RFS, RDS and RES) with ranges from zero to (65535, 1023 and 4095), respectively.

- 2. Calculating randomization parameters for the started switching cycle and the needed number of steps to fulfill them as in the following equations:

$$\mathbf{f}_{\rm sw} = \mathbf{f}_{\rm L} + \mathbf{K} * \mathbf{RFS} \tag{1}$$

$$TN = f_{clk} / f_{sw}$$

(2)

$$WN = TN * (d_L + RDS)/1E4$$

(3)

$$EN = TN * (e_L + RES) / 1E4$$

(4)

## Where;

| $\mathbf{f}_{\mathrm{sw}}$ | : Switching frequency                                                                                              |

|----------------------------|--------------------------------------------------------------------------------------------------------------------|

| $\mathbf{f}_{\mathrm{L}}$  | : Lower frequency limit, (taken 234.5 kHz)*                                                                        |

| K                          | : Constant (taken K=2*) for achieving the required randomized frequency range (234.5~365.5 kHz)*                   |

| RFS, RDS,<br>and RES       | : Pseudorandom output streams converted into integer numbers                                                       |

| TN                         | : Needed number of steps to fulfill the switching frequency                                                        |

| $\mathbf{f}_{clk}$         | : Clock frequency                                                                                                  |

| WN                         | : Needed number of steps to fulfill the duty-ratio                                                                 |

| $d_{\rm L}$                | : Lower duty-ratio limit, (taken 2488)*                                                                            |

| EN                         | : Needed number of steps to fulfill the pulse position                                                             |

| e <sub>L</sub>             | : Lower pulse position limit, (taken 1500)*<br>: For normalizing both of ( $d_L$ +RDS) and ( $e_L$ +RES) to be a   |

| 1E4                        | fraction of one, (since their maximum values have been considered as 1E4).                                         |

| *: For case RR             | RM, (F <sub>k</sub> =234.5~365.5 kHz, d <sub>k</sub> =0.249~0.351 and $\epsilon_k$ =0.15~0.56 of T <sub>k</sub> ). |

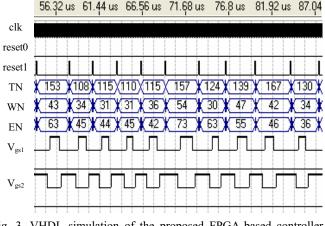

Generating the digital pulse-width 3. modulated waveforms (V<sub>gs1,2</sub>) with the commanded randomization parameters. As shown in Fig. 3, the designed DPWM uses a clocked-counter that increments (up to TN) and resets at the end of every switching cycle of the PWM (see reset1 signal). When the counter value lies between the reference values {EN, EN+WN}, the controller keeps the PWM output state high, else low. In this way, the digital pulse-width modulated waveforms  $(V_{gs1,2})$  are generated with the commanded randomization parameters.

Fig. 3. VHDL simulation of the proposed FPGA-based controller with RRRM scheme.

# IV. EXPERIMENTAL VERIFICATION

All the spread-spectrum schemes, described previously, have been designed and implemented using an Altera FPGA. A synchronous buck converter topology has been selected in order to improve efficiency and reduce heat loss. The output inductor and capacitor have been sized such that the converter operates in continuous conduction mode (CCM). Table II illustrates the converter power-circuit parameters.

| THE CONVERTER POWER-CIRCUIT PARAMETERS. |                                  |       |  |  |  |

|-----------------------------------------|----------------------------------|-------|--|--|--|

| Symbol                                  | Description                      | Value |  |  |  |

| V <sub>in</sub>                         | Input voltage (V)                | 12    |  |  |  |

| Vo                                      | Output voltage (V)               | 3.3   |  |  |  |

| Io                                      | Output current (A)               | 5     |  |  |  |

| $f_{csw}$                               | Center switching frequency (kHz) | 300   |  |  |  |

| L                                       | Output inductor (µH)             | 4.3   |  |  |  |

| С                                       | Output capacitor (µF)            | 470   |  |  |  |

| C <sub>in</sub>                         | Input capacitor (µF)             | 100   |  |  |  |

TABLE II

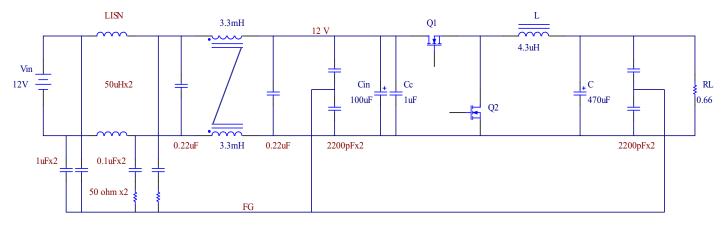

Fig. 4. Experimental circuit for conducted-noise measurements.

The conducted-noise has been measured across the input terminals of the converter using line impedance stabilization networks (LISN), [5]. Fig. 4 describes Experimental circuit for conducted-noise measurements. The LISN is used to standardize the input impedance seen from the converter input and sense the conducted-noise, which is measured by an EMI receiver. Noise measurements have been taken at:  $V_{in} = 12 \text{ V}, V_o = 3.3 \text{ V}, \text{ and } I_o = 5 \text{ A}.$

#### V. RESULTS AND DISCUSSION

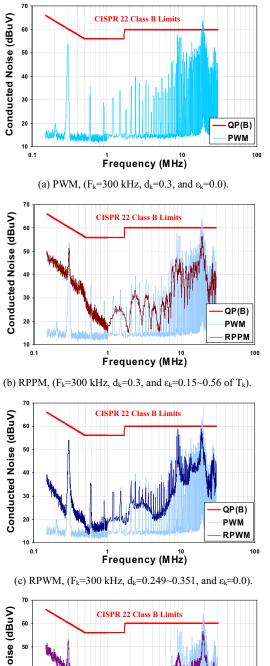

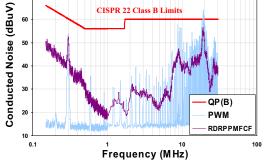

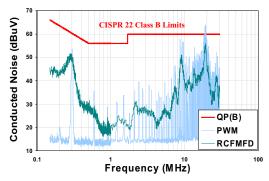

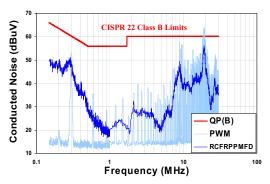

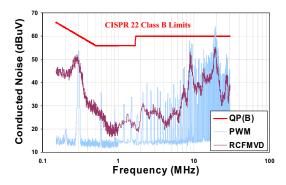

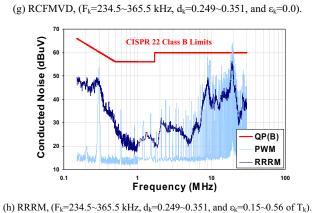

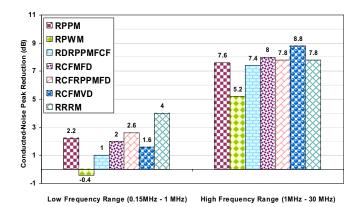

Fig. 5 illustrates the measured conducted-noise spectrum of the converter with different spread-spectrum schemes. It is clear that the noise peaks are concentrated in two regions; the first region at the low frequency range  $(0.15 \sim 1 \text{ MHz})$  around the center switching frequency, and the other region at the high frequency range  $(1 \sim 30 \text{ MHz})$ .

Comparing Fig. 5.(b ~ d) with Fig. 5.(e ~ h) reveals that the switching frequency, as a randomization parameter, is more efficient in spreading the conducted-noise than the duty-ratio or the pulse position parameters.

Fig. 6 presents the effect of the spread-spectrum schemes on the conducted-noise peak reduction at both low and high frequency ranges. This comparison has been carried-out by subtracting the conducted-noise peak of the PWM scheme from that of the spread-spectrum scheme, at both of the two regions. It can be seen that the RCFRPPMFD and RCFMVD schemes achieve a similar performance.

The RPWM scheme gives the worst performance. It poorly improves the conducted-noise spectrum at the high frequency range. Moreover, it increases the conducted-noise peak at the low frequency range. However, the RRRM scheme attains the best performance. It provides the highest conducted-noise peak reduction at the low frequency range. Furthermore, it decreases the conducted-noise peak at the high frequency range by 7.8dB.

## VI. CONCLUSIONS

Many spread-spectrum schemes, several of which are new, have been designed and implemented using FPGA for conducted-noise reduction in DC-DC converters. Moreover, the effect of using such schemes on the conducted-noise characteristics of the converter has been experimentally investigated. It can be concluded that:

- 1. The RPWM scheme gives the worst performance. It poorly improves the conducted-noise spectrum at the high frequency range. Moreover, it increases the conducted-noise peak at the low frequency range.

- 2. The switching frequency, as a randomization parameter, is more efficient in spreading the conducted-noise than the duty-ratio or the pulse position parameters.

- 3. The RRRM scheme attains the best performance. It provides the highest conducted-noise peak reduction at the low frequency range. Furthermore, it decreases the conducted-noise peak at the high frequency range by 7.8dB.

Currently, a detailed study of the RRRM scheme is being carried-out by the authors. It includes calculation/estimation of the noise spectrum, and sweeping the three randomization parameters for reaching the values which achieve the best conducted-noise spectrum spreading.

(d) RDRPPMFCF, (F<sub>k</sub>=300 kHz,  $d_k$ =0.249~0.351, and  $\epsilon_k$ =0.15~0.56 of T<sub>k</sub>).

(e) RCFMFD, (F<sub>k</sub>=234.5~365.5 kHz, d<sub>k</sub>=0.3, and  $\epsilon_k$ =0.0).

(f) RCFRPPMFD, (F\_k=234.5~365.5 kHz, d\_k=0.3, and  $\epsilon_k$ =0.15~0.56 of Tk).

Fig. 6. The effect of the spread-spectrum schemes on the conductednoise peak reduction.

#### REFERENCES

- L. Palma, M. H. Todorovic, and P. Enjeti, "Design Considerations for a Fuel Cell Powered DC-DC Converter for Portable Applications", Applied Power Electronics Conference and Exposition (APEC '06), pp. 1263-1268, Mar 2006.

- [2] A. P. Dancy and A. P. Chandrakasan, "Ultra Low Power Control Circuits for PWM Converters", IEEE Power Electronics Specialists Conference (PESC'97), pp. 21-27, 1997.

- [3] A. Boni, A. Carboni, and A. Facen, "Design of Fuel-Cell Powered DC-DC Converter for Portable Applications in Digital CMOS Technology", 13th IEEE International Conference on Electronics, Circuits and Systems (ICECS '06), pp: 212 - 215, Dec 2006.

- [4] T. Ninomiya, M. Shoyama, C. Jin, and G. Li, "EMI Issues in Switching Power Converters", Proceedings of the 13th International Symposium on Power Semiconductor Devices and ICs (ISPSD'01), Osaka, Japan, pp. 81-85, 2001.

- [5] C.R. Paul, "Introduction to Electromagnetic Compatibility", John Wiley & Sons, New York, 2nd edition, 2006.

- [6] Devender, K. Nageswara Rao, K. Suryanarayana, S. Sarvade, and D. Ramesh, "Electromagnetic Interference (EMI) Suppression Techniques—A Case Study", Proceedings of the International Conference on Electromagnetic Interference and Compatibility, pp. 221-225, 2002.

- [7] T. Tanaka, T. Ninomiya, and K. Harada, "Random-Switching Control in DC-to-DC Converters", IEEE PESC'1989, vol. 1, pp. 500 - 507, Jun 1989.

- [8] T. Ninomiya, T. Tanaka, H. Kameda, and K. Harada, "Noise Reduction of Switching-Mode Power Converters by Randomswitching Control", Proceedings of IPEC-Tokyo'90, pp. 1165 - 1172, Apr 1990.

- [9] T. Tanaka, H. Kameda, and T. Ninomiya, "Noise Analysis of DC-to-DC Converter with Random-switching Control", Proceedings of INTELEC'91, pp. 283 - 290, Nov 1991.

- [10] A. M. Stankovic, G. C. Verghese, and D. J. Perreault, "Analysis and Synthesis of Randomized Modulation Schemes for Power Converters", IEEE Trans. Power Electron., vol. 10, pp. 680 - 693, Nov 1995.

- [11] T. Tanaka, H. Hamasaki, and H. Yoshida, "Random-Switching Control in DC-to-DC Converters: An Implementation Using Msequence", INTELEC'97, pp 431 – 437, Oct 1997.

- [12] K. K. Tse, H. S. Chung, S. Y. R. Hui, and H. C. So, "A Comparative Investigation on the Use of Random Modulation Schemes for DC/DC Converters", IEEE Trans. Ind. Electron., vol. 47, no. 2, pp. 253–263, Apr. 2000.

- [13] F. Mihali, and D. Kos, "Reduced Conductive EMI in Switched-Mode DC-DC Power Converters without EMI Filters: PWM Versus Randomized PWM", IEEE Trans. Power Electron., vol. 21, no. 6, pp. 1783 - 1794, Nov 2006.

- [14] G. M. Dousoky, M. Shoyama, and T. Ninomiya, "Conducted-Noise Reduction of Randomly Switched Buck Converter Using FPGA", IEICE Technical Report, vol. 108, no. 25, pp 45-50, May 2008.

- [15] O. Trescases, G. Wei, A. Prodic, and W. T. Ng, "An EMI Reduction Technique for Digitally Controlled SMPS", IEEE Trans. Power Electron., vol. 22, no. 4, pp. 1560 - 1565, July 2007.

- [16] "What Is the Next Implementation Fabric?", IEEE Design and Test of Computers ,vol. 20, no. 6, pp. 86-95, Nov/Dec, 2003.

- [17] E. Monmasson, and M. N. Cirstea, "FPGA Design Methodology for Industrial Control Systems—A Review", IEEE Trans. Ind. Electron., vol. 54, no. 4, pp. 1824–1842, August. 2007.