# 5MHz PWM-Controlled Current-Mode Resonant DC-DC Step-Down Converter Using GaN-HEMTs

Akinori Hariya

Student Member, IEEE Nagasaki University 1-14 Bunkyo-machi, Nagasaki-shi, Nagasaki, Japan bb52312202@cc.nagasaki-u.ac.jp

Satoshi Tomioka

TDK-Lambda Corporation 2704-1 Settaya-machi, Nagaoka-shi, Nigata, Japan s.tomioka@jp.tdk-lambda.com Ken Matsuura

TDK Corporation 2-15-7 Higashiowada, Ichikawa-shi, Chiba, Japan matsuken@jp.tdk-lambda.com

Yoichi Ishizuka Member, IEEE Nagasaki University 1-14 Bunkyo-machi Nagasaki-shi, Nagasaki, Japan isy2@nagasaki-u.ac.jp Hiroshige Yanagi

TDK-Lambda Corporation 2704-1 Settaya-machi, Nagaoka-shi, Nigata, Japan yanagi@jp.tdk-lambda.com

Tamotsu Ninomiya

Fellow, IEEE The International Centre for the Study of East Asian Development 1-8 Hibikino, Wakamatsu-ku Kitakyushu-shi, Fukuoka, Japan t\_ninomiya@icsead.or.jp

Abstract -- High power efficiency and high power density are required in regulated isolated DC-DC converters. In this paper, a novel pulse width modulation (PWM) control method which is suitable for the isolated current-mode resonant DC-DC converter operated at MHz level switching frequency is proposed. The output voltage with the proposed method can be regulated with no additional components at fixed switching frequency. In addition, zero voltage switching (ZVS) of primaryside switches at turn-on can be maintained. The principle of the proposed method and the method of ZVS operation in the proposed method are explained.

Some experiments have been performed with a 5MHz isolated step-down DC-DC converter using Gallium Nitride High Electron Mobility Transistors (GaN-HEMTs); the output voltage is 12V and the total volume of the circuit is 16.14cm<sup>3</sup>. With the proposed PWM control method, input voltage range is 42-45.5V, and maximum load current range is 10A at  $V_i = 45.5V$ . The ZVS of the primary-side switches at turn-on is confirmed in all experimental regions, and the maximum power efficiency is 89.2%.

*Index Terms*— DC-DC power converters, Gallium nitride, Pulse width modulation converters, Switching converters, Zero voltage switching.

# I. INTRODUCTION

Recently, high power efficiency and high power density power conversion systems have been required in information and communication technology (ICT) equipment due to increases in system power consumption. Therefore, intermediate bus architectures (IBAs) have been introduced in this field in recent years [1]. The performances of three basic IBAs are investigated in [2]. The literature reported that the double regulated IBA has the potential of the best performance. This architecture is composed of a regulated bus converter and regulated point of load (POL) converters. An isolated step-down DC-DC converter is used as the bus converter in IBA. The rated input voltage is 48V, and the output target voltage is 12V which is the intermediate bus voltage. At the next stage of bus conversion, 12V is regulated in POLs to e.g. 2.5 or 1.0V required by each load. In this architecture, the design of the regulated bus converter is especially difficult due to requirements both of isolation and regulation. Thus, research of regulated bus converters is important for more improvement of the double regulated IBA. In this paper, a 5MHz PWM-controlled current-mode resonant DC-DC step-down converter for regulated bus converters is discussed.

Corresponding to the requirement of high power density, the increase in the switching frequency of these converters has been considered to be one of the key approaches. Therefore, a 5MHz switching frequency, which is relatively high for isolated DC-DC converters, is adopted in this research [3]-[5]. However, by adopting a high switching frequency, power loss such as switching loss and gate driving loss increases. To solve this problem, the current-mode resonant DC-DC converter is used because this converter can reduce switching loss. Also, GaN-HEMTs are suitable for high switching frequency operation as semiconductor switches because of low gate driving loss.

The output voltages of current-mode resonant DC-DC converters are usually controlled by pulse frequency modulation (PFM). However, PFM controlled current-mode resonant DC-DC converter are not suitable for miniaturization. The details are described in section III.

The novel PWM control method which is suitable for the isolated current-mode resonant DC-DC converter operated at MHz level switching frequency is proposed. This converter topology is the same as the conventional current-mode resonant DC-DC converter with synchronous rectification. In general, when load current increases or input voltage decreases from rated input voltage, the output voltage is decreased. Therefore, to maintain constant output voltage, boost conversion is needed. The proposed PWM control method can regulate output voltage without any additional

components. By using the transformer's leakage inductance and secondary-side synchronously rectifying switches, secondary-side boost conversion operation can be realized. In MHz level switching operation for high power density, switching loss increases dramatically. To suppress switching loss, ZVS operation is needed. The proposed PWM control method can maintain ZVS of primary-side switches at the turn-on in all operating regions.

The targets of the research are to obtain the high performances which are small volume, 42-53V input voltage range, which is used in information servers and other computer applications [6], 10A of maximum load current range, and the realization of ZVS of primary-side switches at turn-on.

In section II, the approach of the realization of DC-DC converter operated at MHz level switching frequency is described. In section III, the issue of the conventional PFM-controlled current-mode resonant DC-DC converter is revealed. In section IV, the proposed PWM-controlled current-mode resonant DC-DC converter is explained. In section V, the experimental results are demonstrated.

# II. THE APPROACH OF THE REALIZATION OF DC-DC CONVERTER OPERATED AT MHZ LEVEL SWITCHING FREQUENCY

For miniaturization of the DC-DC converter, the increase in the switching frequency is considered to be one of the key approaches.

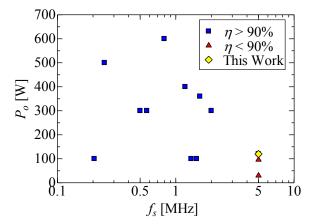

As shown in Fig. 1, there are not many reports in the literature for the region of over 5MHz switching frequency and 100W output power with more than 90% of power efficiency. Therefore, this research challenges 5MHz of switching frequency at 120W of output power. To suppress increasing core power loss with high switching frequency, NiZn ferrite core is used [18]. To increase power density, a multilayer printed circuit board (PCB) is employed in this research. The details of PCB layout technique is shown in [4]. Also, to increase more power density, a planar transformer is employed in the research. The planar transformer is directly manufactured with multi-layered pattern in the PCB.

In the prototype circuit, conventional hard-switched gate driving is used for the GaN-HEMTs. Therefore, the gate driving loss  $P_d$  is expressed by

$$P_d = Q_G V_{GS} f_s \tag{1}$$

where  $Q_G$  is gate charge,  $V_{GS}$  is gate-to-source voltage of GaN-HEMT, and  $f_s$  is switching frequency. From eq. (1), this power loss is proportional to  $f_s$ .

For reducing gate driving loss, GaN-HEMTs are adopted in this research because GaN-HEMTs have low  $Q_G$  and be driven at low gate-to-source voltage. The benefits of GaN-HEMTs are not purely low  $Q_g$ , but a physically smaller transistor for a given low drain-to-source on resistance  $R_{ds(on)}$ and  $V_{gs}$  blocking capability. Due to physically smaller device with lower parasitic capacitances, faster device switching speed results. Additionally, GaN-HEMTs have no source-todrain recovery charge [19] and low package inductance

Fig. 1. The performances of isolated DC-DC converters which have 48V of input voltage and 12V of output voltage in the previous papers presented at APEC from 2014 to 2010 and ECCE from 2013 to 2009 [4], [5], [7]-[17].

because of small package size [20]. Other researches have validated the effectiveness of GaN-HEMTs for high switching frequency DC-DC converters [7]-[10], [14]. Also, GaN-HEMTs have been proved more effective than silicon devices in [7], [9]-[11], [13].

However, because of GaN-HEMTs having low gate-tosource threshold voltage  $V_{th}$ , low maximum gate-to-source voltage  $V_{GSS}$ , and high source-to-drain voltage  $V_{SD}$ , it is difficult to drive GaN-HEMTs. Therefore, suitable drive circuit for GaN-HEMTs is needed. Some literatures show that driver LM5113 is suitable for driving GaN-HEMTs [21].

By adopting a high switching frequency, switching loss increases dramatically. However, if switches can achieve softswitching such as ZVS operation at the turn-on, the switching loss can be suppressed to almost zero. In this research, current-mode resonant DC-DC converter topology featuring ZVS of primary-side switches at turn-on is adopted. Many studies of this circuit topology in MHz level switching operation have been done [7], [10], [14].

# III. THE ISSUE OF THE CONVENTIONAL PFM-CONTROLLED CURRENT-MODE RESONANT DC-DC CONVERTER

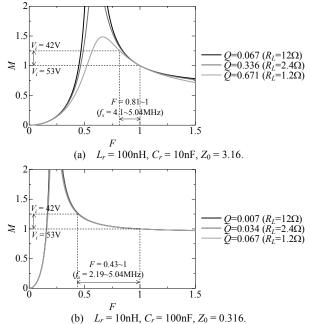

To reduce the volume of the DC-DC converter, the resonant inductance of the converter needs to be minimized. For effective miniaturization of the converter, the miniaturization of resonant inductance is important. Meanwhile, to reduce the switching loss, the current-mode resonant DC-DC converter is widely used [7], [10], [12]-[17], [22], [23]. Generally, the current-mode resonant DC-DC converter is controlled by PFM control which varies switching frequency. In Fig. 2, the relation of resonant inductance and frequency variance is shown.  $L_r = 100$ nH and  $L_r = 10$ nH are in Fig. 2 (a) and (b), respectively. The other parameters are  $V_i = 48$ V, n = 2.2,  $L_m = 200$ nH.

In this figure, the definitions of the converter parameters are

$$M = \left(2nV_o\right)/V_i , \qquad (2)$$

$$\kappa = L_m / L_r , \qquad (3)$$

$$F = f_s / f_0 , \tag{4}$$

$$f_0 = 1/(2\pi\sqrt{L_r C_r}),$$

(5)

$$\omega_0 = 2\pi y_0, \tag{6}$$

$$R_{ac} = \left(8n^2 R_L\right) / \pi^2$$

(8)

and

$$Z_0 = \sqrt{L_r / C_r} \tag{9}$$

where turn ratio *n*, magnetizing inductance  $L_m$ , resonant inductance  $L_r$ , switching frequency  $f_s$ , resonant capacitance  $C_r$  and load resistance  $R_L$ . According to [22], eq. (2) can be converted from eqs. (3) to (8) as (10). Eq. (10) can be

$$M = \frac{1}{\sqrt{\left(1 + \frac{1}{\kappa} \left(1 - \frac{1}{F^2}\right)\right)^2 + Q^2 \left(F - \frac{1}{F}\right)^2}}$$

(10)

It is assumed that input voltage range is from 42 to 53V at  $R_L = 1.2\Omega$  and  $V_o = 12V$ . The influence of  $L_r$  on M can be confirmed from Fig. 2 (a) and (b). In case of  $L_r = 100$ nH, for realization of the range, F is changed from 0.81 to 1. In contrast, in case of  $L_r = 10$ nH, for realization of the range, F is changed from 0.43 to 1.

If large resonant inductance value is used, the region of switching frequency is narrow, which leads to small size noise filter. However, to obtain large resonant inductance value, the physical size of the inductor becomes large. If small resonant inductance value is used, the region of switching frequency is wide, which leads to large size noise filter. There is a tradeoff between the size of the required noise filter and resonant inductor.

As the result, for the miniaturization of the DC-DC converter, it is shown that pure PFM control is not appropriate. Therefore, PWM-controlled current-mode resonant DC-DC conversion has been proposed [3], [5].

### IV. THE PROPOSED PWM-CONTROLLED CURRENT-MODE RESONANT DC-DC CONVERTER

In the previous researches, some PWM-controlled currentmode resonant DC-DC converters have been presented [24]-[26]. For example, the method of additional auxiliary circuits for regulating output voltage [24], [25], and the method of controlling the duty ratio of primary-side switches [26] have been proposed. However, these methods need some additional components for regulating output voltage. On the other hand, the output voltage of the proposed current-mode resonant DC-DC converter can be controlled without any additional components at fixed switching frequency. In addition, ZVS of primary-side switches at turn-on can be accomplished in the proposed method. In this section, the principle of the proposed method and the method for achieving ZVS turn-on are explained.

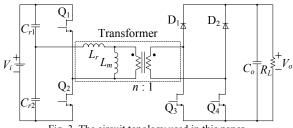

Fig. 3. The circuit topology used in this paper.

### A. The Circuit Topology

The circuit topology is based on a half-bridge type currentmode resonant DC-DC converter as shown in Fig. 3. The primary-side is the half-bridge topology.  $Q_1$  and  $Q_2$  are driven in 50% duty ratio, alternatively.  $C_{r1}$  and  $C_{r2}$  are the resonant capacitors which have the same capacitance and also make averaged voltage of  $v_c$  to one half of the input. The inside of the broken line is the equivalent circuit of the magnetic transformer, where  $L_r$  is leakage inductance, and  $L_m$  is the transformer's magnetizing inductance. The turn ratio is n : 1.  $L_r$  is used as the resonant inductance. The secondary-side is the full-bridge topology composed with diodes  $D_1$  and  $D_2$  for high-side arm switches, and transistors  $Q_3$  and  $Q_4$  for low-side arm switches.

### B. The Principle of the Proposed PWM Control Method

To simplify analysis of the circuit operation, the following assumptions are made:

- GaN-HEMTs are treated as ideal switches;

- The reverse-conduction voltage drops of the primaryside switches are neglected;

• Because of the gate is shorted to the source by the gate drivers during off-term, drain-to-gate capacitance therefore appear in parallel with drain-to-source capacitance of each GaN-HEMTs. Therefore, the capacitances of the primary-side GaN-HEMTs which labeled  $C_{oss1}$  and  $C_{oss2}$  are defined as the sum of the drain-to-gate capacitance and the drain-to-source capacitance during off-term, respectively. These capacitances are assumed as  $C_{oss1} = C_{oss2}$  and

$$C_{oss} = C_{oss1} + C_{oss2};$$

- Resonant capacitances are satisfied  $C_{r1} = C_{r2}$ ,  $C_r = C_{r1} + C_{r2}$ ;

- The forward voltage drops and the parasitic capacitances

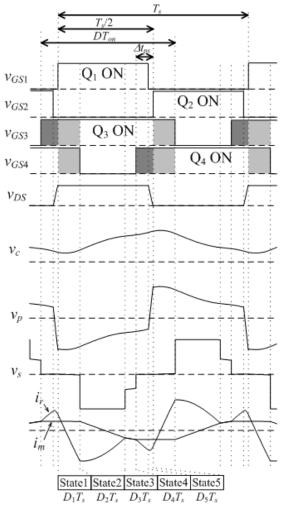

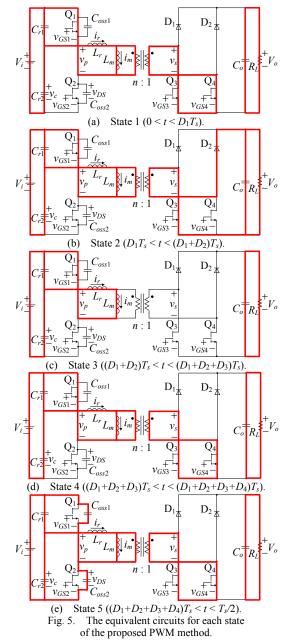

Fig. 4. The operational waveforms of the proposed PWM control.

TABLE I. CIRCUIT OPERATION STATES

| State   | FET |     |    |     | Diode          |     |

|---------|-----|-----|----|-----|----------------|-----|

|         | Q1  | Q2  | Q3 | Q4  | D <sub>1</sub> | D2  |

| State 1 | ON  | OFF | ON | ON  | OFF            | OFF |

| State 2 | ON  | OFF | ON | OFF | OFF            | ON  |

| State 3 | ON  | OFF | ON | OFF | OFF            | OFF |

| State 4 | ON  | OFF | ON | ON  | OFF            | OFF |

| State 5 | OFF | OFF | ON | ON  | OFF            | OFF |

of the secondary-side diodes are neglected;

- The output capacitances and the reverse-conduction voltage drops of the secondary-side switches are neglected;

- The output voltage is constant;

The output voltage can be controlled by changing the duty ratio of  $Q_3$  and  $Q_4$ , simultaneously. When the duty ratio is less than 0.5, the circuit operates as well as conventional current resonance circuit. When the duty ratio is more than 0.5, the circuit operates in the proposed operation.

The operational waveforms are shown in Fig. 4. The circuit operation is separated into 10 states in the proposed method. First half switching cycle is from state 1 to 5. Second half switching cycle is the remaining states. The second half switching cycle is symmetrical in operation to the first half

switching cycle. Therefore, because same analytical results can be obtained in each switching cycle, the description for the second half switching cycle is omitted. The switch combination is shown in TABLE I. The equivalent circuits for each state of a half switching term are shown in Fig. 5. In this figure, the switches drawn with weak colors represent OFF, and red line represents current flow.

The definitions of the duty ratio D are followed as

$$D = T_{on}/T_s , \qquad (11)$$

$$D = 1/2 + D_1 + D_4 + D_5, (12)$$

$$D_1 + D_2 + D_3 + D_4 + D_5 = 1/2 \tag{13}$$

and

$$\begin{cases}

D \le 0.5 \dots (\text{conventional operation}) \\

D > 0.5 \dots (\text{proposed operation})

\end{cases}$$

(14)

where  $T_s$  is the switching period, and  $T_{on}$  is the on-term of  $Q_3$  and  $Q_4$ .  $D_1 \sim D_5$  are the duty ratio of each state. The definitions of the resonant operation are as follows;

$$\omega_1 = 1 / \sqrt{(L_r + L_m)C_r} , \qquad (15)$$

$$Z_1 = \sqrt{(L_r + L_m)/C_r}$$

(16)

and

$$\omega_{oss} = 1 / \sqrt{L_r C_{oss}} \tag{17}$$

The definitions of the initial value of the variables are as follows;

$$v_{c1}(0) = V_i / 2 - V_c$$

(18)

$$i_{r1}(0) = I_r$$

(19)

The descriptions for each state are described below.

State 1 ( $0 < t < D_1T_s$ ):

In this state,  $t_1$  is defined as  $t_1 = t$ . The primary-side switch  $Q_1$  is turned ON. Also, the secondary-side switches both  $Q_3$ and  $Q_4$  are turned ON.  $Q_3$  and  $Q_4$  are overlapped as indicated with the light gray area in Fig. 4. The resonant inductance  $L_r$ is magnetized by  $i_r$  for boosting output voltage. From the figure,  $v_{c1}(t_1)$  and  $i_{r1}(t_1)$  become

$$v_{c1}(t_1) = V_i - \{ (V_i/2 + V_c) \cos(\omega_0 t_1) + Z_0 I_r \sin(\omega_0 t_1) \}$$

(20)

and

$$i_{r1}(t_1) = -1/Z_0 \left( V_i/2 + V_c \right) \sin(\omega_0 t_1) + I_r \cos(\omega_0 t_1).$$

(21)

The final values of the state 1 are

The final values of the state T are

$$V_{c2} = v_{c1} (D_1 T_s)$$

(22)

and

$$I_{r2} = i_{r1} (D_1 T_s).$$

<sup>(23)</sup>

State 2  $(D_1T_s < t < (D_1+D_2)T_s)$ :

In this state,  $t_2$  is defined as  $t_2 = t - D_1 T_s$ . After Q<sub>4</sub> is turned OFF, the direction of the voltage applied to D<sub>2</sub> is inverted, and diode of D<sub>2</sub> becomes ON. The inductance current which is magnetized in state 1 flow through diode  $D_2$  and switch  $Q_3$ , to the load. From the figure,  $v_{c2}(t_2)$  and  $i_{r2}(t_2)$  become

$$v_{c2}(t_2) = V_i - nV_o + (V_{c2} - V_i + nV_o)\cos(\omega_0 t_2) - Z_0 I_{r2}\sin(\omega_0 t_2)$$

(24)

and

$$i_{r2}(t_2) = 1/Z_0 (V_{c2} - V_i + nV_o) \sin(\omega_0 t_2) + I_{r2} \cos(\omega_0 t_2)$$

(25)

The final values of the state 2 are

$$V_{c3} = v_{c2} \left( D_2 T_s \right)$$

(26)

and

$$I_{r3} = i_{r2} \left( D_2 T_s \right). \tag{27}$$

State 3  $((D_1+D_2)T_s < t < (D_1+D_2+D_3)T_s)$ :

In this state,  $t_3$  is defined as  $t_3 = t - D_1 T_s - D_2 T_s$ . The direction of the diode D<sub>2</sub> current is inverted, and diode of D<sub>2</sub> becomes OFF. In the state, resonant current  $i_r$  equal to magnetizing current  $i_m$ . From the figure,  $v_{c3}(t_3)$  and  $i_{r3}(t_3)$  become

$$v_{c3}(t_3) = V_i + (V_{c3} - V_i)\cos(\omega_1 t_3) - Z_1 I_{r3}\sin(\omega_1 t_3)$$

(28)

and

$$i_{r_3}(t_3) = 1/Z_1 \left( V_{c_3} - V_i \right) \sin(\omega_1 t_3) + I_{r_3} \cos(\omega_1 t_3).$$

(29)

The final values of the state 3 are

$$V_{c4} = v_{c3} (D_3 T_s)$$

(30)

and

$$I_{r4} = i_{r3} (D_3 T_s).$$

(31)

State 4  $((D_1+D_2+D_3)T_s \le t \le (D_1+D_2+D_3+D_4)T_s)$ :

In this state,  $t_4$  is defined as  $t_4 = t - D_1 T_s - D_2 T_s - D_3 T_s$ . This state is similar to state 1. In the state, the resonant inductance  $L_r$  is magnetized by  $i_r$  for ZVS of the primary-side switch at turn-on. Q<sub>3</sub> and Q<sub>4</sub> are overlapped as indicated with the dark gray area in Fig. 4. From the figure,  $v_{c4}$  ( $t_4$ ) and  $i_{r4}$  ( $t_4$ ) become

$v_{c4}(t_4) = V_i + (V_{c4} - V_i)\cos(\omega_0 t_4) - Z_0 I_{r4}\sin(\omega_0 t_4) \quad (32)$ and  $(1) = (T - T) \sin(\alpha t) + I$ (

$$i_{r4}(t_4) = 1/Z_0 \left( V_{c4} - V_i \right) \sin(\omega_0 t_4) + I_{r4} \cos(\omega_0 t_4).$$

(33)

The final values of the state 4 are

$V_{4} = v_{4} \left( D_{4} T_{4} \right)$

and

$$(D, T)$$

(21)

(34)

$$I_{r5} = i_{r4} (D_4 T_s).$$

(35)

State 5 ( $(D_1+D_2+D_3+D_4)T_s < t < T_s/2$ ):

In this state,  $t_5$  is defined as  $t_5 = t - D_1 T_s - D_2 T_s - D_3 T_s - D_4 T_s$ . The primary-side switch Q<sub>1</sub> is turned OFF. All primary-side switches are turned OFF, called dead time. The parasitic capacitor  $C_{oss1}$  of  $Q_1$  is discharged by a half of resonant inductance current  $i_r$ . Q<sub>3</sub> and Q<sub>4</sub> are overlapped as indicated with the dark gray area in Fig. 4. From the figure,  $v_{c5}$  ( $t_5$ ),  $v_{DS5}$  $(t_5)$  and  $i_{r_5}(t_5)$  become

$$v_{c5}(t_5) = V_{c5} - \frac{\omega_0^2 (V_{c5} - V_i)}{\omega_0^2 + \omega_{oss}^2} + \frac{\omega_0^2 (V_{c5} - V_i)}{\omega_0^2 + \omega_{oss}^2} \cos\left(\sqrt{\omega_0^2 + \omega_{oss}^2} \cdot t_5\right) , \qquad (36)$$

$$- \frac{I_{r5}}{C_r \sqrt{\omega_0^2 + \omega_{oss}^2}} \sin\left(\sqrt{\omega_0^2 + \omega_{oss}^2} \cdot t_5\right)$$

$$v_{DS5}(t_{5}) = \frac{\omega_{oss}^{2}(V_{c5} - V_{i})}{\omega_{0}^{2} + \omega_{oss}^{2}} + V_{i}$$

$$-\frac{\omega_{oss}^{2}(V_{c5} - V_{i})}{\omega_{0}^{2} + \omega_{oss}^{2}} \cos\left(\sqrt{\omega_{0}^{2} + \omega_{oss}^{2}} \cdot t_{5}\right)$$

(37)

$$I_{e5} = e_{oss} \left(\sqrt{\omega_{0}^{2} + \omega_{oss}^{2}} \cdot t_{5}\right)$$

$$+\frac{I_{r5}}{C_{oss}\sqrt{\omega_0^2+\omega_{oss}^2}}\sin\left(\sqrt{\omega_0^2+\omega_{oss}^2}\cdot t_5\right)$$

and

$$i_{r5}(t_{5}) = \frac{V_{c5} - V_{i}}{L_{r}\sqrt{\omega_{0}^{2} + \omega_{oss}^{2}}} \cdot \sin\left(\sqrt{\omega_{0}^{2} + \omega_{oss}^{2}} \cdot t_{5}\right) + I_{r5}\cos\left(\sqrt{\omega_{0}^{2} + \omega_{oss}^{2}} \cdot t_{5}\right)$$

(38)

# C. The Method for Achieving ZVS of Primary-side Switches at Turn-On in the Proposed PWM Control

To accomplish ZVS of the primary-side switches at turn-on, small magnetizing inductances  $L_m$  have been used in currentmode resonant DC-DC converters generally. However, small  $L_m$  value leads to increase of primary-side current which can cause a reduction of power efficiency. Therefore, to accomplish ZVS operation in the proposed method, phaseshift between primary and secondary-side switches which controls resonant current is proposed.

As shown in Fig. 4, the proposed operation has phase-shift between primary and secondary-side switches.  $\Delta t_{ps}$  is the time length of the phase-shift. Without the phase-shift,  $\Delta t_{ps} = 0$ ns, the previous state of the dead time becomes discontinuous current state. With this situation, initial current cannot be charged enough for ZVS operation because of secondary-side parasitic capacitances. Therefore, even with the long dead time duration, ZVS cannot be achieved. With the phase-shift, the problem of the initial current can be solved. From eqs. (33) and (35), the initial current of the dead time,  $I_{r5}$  is

$I_{r5} = 1/Z_0 \left( V_{c4} - V_i \right) \sin(\omega_0 D_4 T_s) + I_{r4} \cos(\omega_0 D_4 T_s).$ (39) The term of the phase-shift becomes

$$\Delta t_{ps} = D_4 T_s + D_5 T_s \,. \tag{40}$$

In eq. (40), as defined as the  $D_5T_s$  is fixed, the term of state 4 becomes larger with the increase of  $\Delta t_{ps}$ .  $I_{r5}$  is related to  $\Delta t_{ps}$  almost linearly. As  $I_{r5}$  increases, the amount of electrical charge  $q_{r5}$  which flows in the resonant inductance during dead time becomes larger.

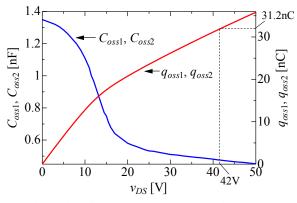

Meanwhile, the output capacitances of GaN-HEMTs are not constant. The value of output capacitance depends on drain-to-source voltage. The influence of drain-to-source voltage on output capacitance is confirmed in [19], as shown in Fig. 6. In considerations of this influence, the initial electrical charge of dead time  $q_{oss}$  is expressed by

$$q_{oss} = \int_0^{v_i} C_{oss}(v_{DS}) \cdot dv_{DS}$$

(41)

From eq. (41), the influence of drain-to-source voltage on  $q_{oss}$  can be obtained, as shown in Fig. 6.

For an example, when input voltage is 42V,  $q_{oss1}$  and  $q_{oss2}$

Fig. 6. The influence of  $v_{DS}$  on  $C_{oss1}$ ,  $C_{oss2}$  and  $q_{oss1}$ ,  $q_{oss2}$ .

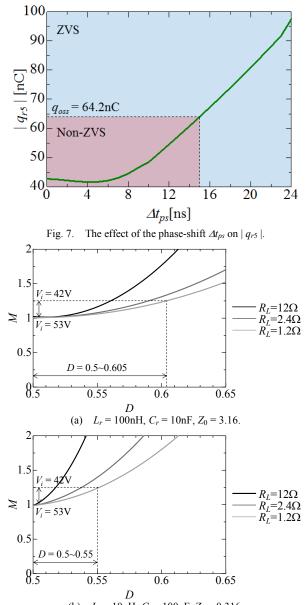

are 32.1nC from Fig. 6. Therefore, equivalent output capacitances  $C_{oss1}$  and  $C_{oss2}$  are 764pF, respectively. In the conditions of  $C_{oss} = 1528$ pF,  $V_i = 42$ V,  $R_L = 20$ hm,  $D_5T_s = 10$ ns, the relation of  $\Delta t_{ps}$  and  $q_{r5}$  are shown in Fig. 7. The electrical charge  $q_{r5}$  can be calculated with

$$q_{r5} = \int_0^{D_5 T_s} i_{r5}(t) dt \tag{42}$$

For achieving ZVS,  $q_{r5}$  has to be larger than the amount of the electrical charge of the output capacitance of the switches as

$$|q_{r5}| > q_{oss} \tag{43}$$

In this case, due to  $q_{oss} = 64.2$ nC, if  $q_{r5}$  is larger than 64.2nC, ZVS operation can be achieved. From the figure, it can be seen that the phase-shift  $\Delta t_{ps}$  between primary and secondary-side switches are valid for ZVS operation in the proposed PWM control.

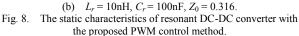

# D. The Static Characteristics of the Proposed Method at MHz Level Operation

Similar to section III, two examples of the static characteristics of the proposed PWM controlled current-mode resonant DC-DC converter are shown in Fig. 8.  $L_r = 100$ nH and  $L_r = 10$ nH are in Fig. 2 (a) and (b), respectively. The other parameters are  $V_i = 48$ V, n = 2.2,  $L_m = 200$ nH.

It is assumed that input voltage range is from 42 to 53V at  $R_L = 1.2\Omega$  and  $V_o = 12V$ . In case of  $L_r = 100$ nH, for realization of the range, D is changed from 0.5 to 0.605. In contrast, in case of  $L_r = 10$ nH, for realization of the range, D is changed from 0.5 to 0.55. By comparing between two parameters, the case of  $L_r = 10$ nH can control in narrow duty ratio than the other one. Therefore, the proposed PWM control method is seen to be suitable for the miniaturization of the DC-DC converter because the output voltage can be controlled with small resonant inductance.

#### V. EXPERIMENTAL RESULTS

In this section, it can be confirmed the difference between the experimental results of the proposed method and the targets of the research.

### A. The Experimental Conditions

As a prototype digital controller, a field programmable gate array (FPGA) Cyclone IV is used, which generates individual gate signal for each switch. The on-terms of the gate signals are manually changed with software. The resolution of the gate signals is 1 nano second.

Some experiments have been performed with parameters as shown in TABLE II. Components used in the experiment are shown in TABLE III.

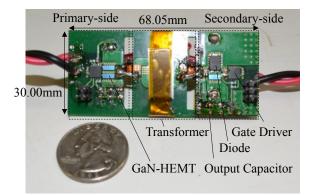

The prototype 5MHz isolated DC-DC converter with GaN-HEMTs is shown in Fig. 9. The total volume of the prototype circuit is 16.14 cm<sup>3</sup>.

TABLE II. EXPERIMENTAL PARAMETERS

| Specifications                            | Value  |

|-------------------------------------------|--------|

| Input voltage: $V_i$                      | 48V    |

| Transformer ratio $n: 1$                  | 2:1    |

| Switching frequency: $f_s$                | 5MHz   |

| Transformer leakage inductance: $L_r$     | 37nH   |

| Transformer magnetizing inductance: $L_m$ | 200nH  |

| Resonant capacitor: $C_{r1}, C_{r2}$      | 15.5nF |

| Output capacitor: $C_o$                   | 18.8µF |

| TABLE III.                   | EXPERIMENTAL COMPONENTS |                             |  |  |

|------------------------------|-------------------------|-----------------------------|--|--|

| Name                         | Manufacture             | Part Name/ Material         |  |  |

| Primary-side<br>GaN-HEMT     | EPC                     | EPC2001                     |  |  |

| Secondary-side<br>GaN-HEMT   | EPC                     | EPC2015                     |  |  |

| Gate Driver                  | TEXAS<br>INSTRUMENTS    | LM5113                      |  |  |

| Diode                        | DIODES                  | PDS1040L                    |  |  |

| Transformer Core<br>Material | TDK                     | SY22<br>(NiZn Ferrite Core) |  |  |

| Resonant Capacitor           | TDK                     | C1608C0G1H392J              |  |  |

| Input Capacitor              | TDK                     | C3216X7R1H105K              |  |  |

| Output Capacitor             | TDK                     | C2012X7R1E475M              |  |  |

| FPGA                         | Terasic<br>(ALTERA)     | DE0-nano<br>(Cyclone IV)    |  |  |

| Isolator                     | TEXAS<br>INSTRUMENTS    | ISO722                      |  |  |

| Current Transformer          | EPCOS                   | B82801B                     |  |  |

Fig. 9. The prototype of the DC-DC converter.

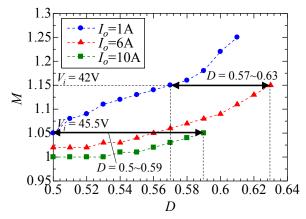

Fig. 10. The open loop static characteristics of resonant DC-DC converter with the proposed PWM control method.

#### B. The Performance of the Proposed Method

The open loop static characteristics of the 5MHz PWMcontrolled DC-DC converter are exhibited as shown in Fig. 10. From the figure, it can be seen that M is controlled by duty ratio D. The range of M from 1.05 to 1.15 corresponds to the range of input voltage from 42 to 45.5V at  $V_o = 12V$ . Thus, by using the proposed PWM control technique, it can be found that the lower input voltage range limitation 42V of the target can be achieved. At M = 1.05, load current can be changed from 1 to 10A while maintaining  $V_o = 12V$ , when changing D from 0.5 to 0.59. The difference between the targets and these results is due to the limitation of PWM and input voltage. In future work, the optimization of the turn ratio, resonant components and control technique will be discussed for expanding input voltage and load current range.

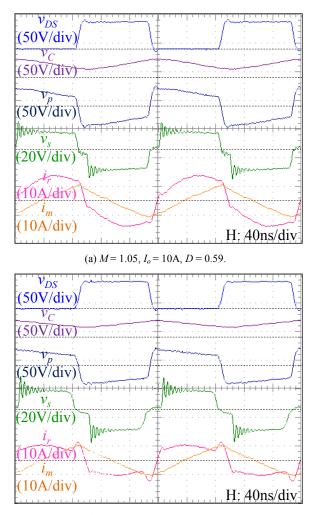

The waveforms of the proposed method are shown in Fig. 11. The magnetizing current  $i_m$  are derived from resonant current  $i_r$  and secondary-side current. The conditions of waveforms (a) and (b) are M = 1.05,  $I_o = 10A$  and M = 1.15,  $I_o = 6A$ , respectively. From the drain-to-source voltage, ZVS of primary-side switches at turn-on seems to be achieved

(b) M = 1.15,  $I_o = 6A$ , D = 0.63. Fig. 11. Experimental waveforms of resonant DC-DC converter with the proposed PWM control method.

during dead time.

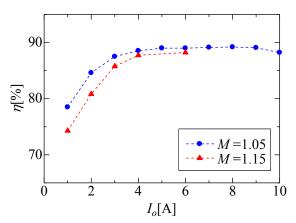

The power efficiency of the DC-DC converter is shown in Fig. 12. The maximum power efficiency is 89.2%. ZVS operation has been confirmed in the range of the experimental conditions.

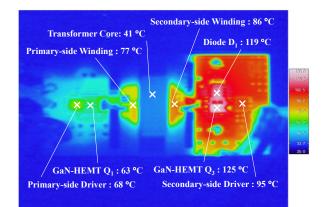

The temperature distribution of the prototype DC-DC converter as shown in Fig. 13, has been taken at M = 1.05 and  $I_o = 10A$ . From the results, the temperature of the secondary-side is in high level, due to hard switching of the secondary-side switches. However, the power loss of the hard-switched switches in secondary-side is suppressed by using lower maximum voltage rating GaN-HEMTs of which  $R_{ds(on)}$  is lower than that of primary-side GaN-HEMTs. Meanwhile, the primary-side temperature is relatively low because of achieving ZVS operation.

#### VI. CONCLUSIONS

In this paper, the principle of the proposed PWMcontrolled current-mode resonant DC-DC step-down converter operated at MHz level switching frequency for high

Fig. 12. The power efficiency of resonant DC-DC converter with the proposed PWM control method.

Fig. 13. The temperature distribution that temperature region is from 20°C to 130°C of resonant DC-DC converter with the proposed PWM control method at M = 1.05,  $I_o = 10$ A, D = 0.59.

power density is presented. By using the proposed method, the output voltage can be regulated without any additional components at fixed switching frequency. Furthermore, ZVS of primary-side switches at turn-on can be accomplished with the proposed phase-shift between primary and secondary-side switches.

The targets of the study is to obtain the high performances which is the small volume, 42-53V input voltage range, 10A maximum load current range, the realization of ZVS of primary-side switches at turn-on in all operating regions.

Some experiments have been performed with a 5MHz isolated DC-DC step-down converter which has GaN-HEMTs, and the total volume of the circuit is 16.14cm<sup>3</sup>. With the proposed PWM control method, input voltage range is 42-45.5V, and maximum load current range is 10A at 45.5V. The ZVS of primary-side switches at turn-on is confirmed, and the maximum power efficiency is 89.2%.

As the future work, to expand the input voltage range and the load current range with high power efficiency, the optimization of the turn ratio, resonant components and control technique will be discussed. Furthermore, feedback control which has high resolution by digital controller is under consideration.

#### ACKNOWLEDGMENT

The authors would like to thank Prof. Hirotoshi Fukunaga, Nagasaki University, for his advice. Also, we would like to thank Mr. Shohei Iwasaki, Technical staff of Nagasaki University, for his technical support.

#### REFERENCES

- [1] L. Brush, "Distributed Power Architecture Demand Characteristics," in *Proc. 2004 IEEE Applied Power Electronics Conf.*, pp. 342-345.

- [2] D. F. D. Tan, "A Review of Immediate Bus Architecture: A System Perspective," *IEEE Journal of Emerging and Selected Topics in Power Electron.*, vol. 2, pp. 363-373, Sep. 2014.

- [3] A. Hariya, K. Matsuura, H. Yanagi, S. Tomioka, Y. Ishizuka, and T. Ninomiya, "High Frequency PWM-Controlled Current-Mode Resonant DC-DC Converter with Boost Conversion," in *Proc. Power Electronics and Applications*, 2013 15th European Conf., pp. 1-10.

- [4] K. Matsuura, H. Yanagi, S. Tomioka, and T. Ninomiya, "Power-Density Development of a 5MHz-Switching DC-DC Converter," in *Proc. 2012 IEEE Applied Power Electronics Conf.*, pp. 2326-2332.

- [5] A. Hariya, K. Matsuura, H. Yanagi, S. Tomioka, Y. Ishizuka, and T. Ninomiya, "5MHz PWM-Controlled Current-Mode Resonant DC-DC Converter with GaN-FETs," in *Proc. 2014 IEEE Applied Power Electronics Conf.*, pp. 1426-1432.

- [6] Y. Ren, M. Xu, J. Sun, and F. C. Lee, "A Family of High Power Density Unregulated Bus Converters," *IEEE Trans. Power Electron.*, vol. 20, pp. 1045-1054, Sep. 2005.

- [7] D. Reusch and J. Strydom, "Evaluation of Gallium Nitride Transistors in High Frequency Resonant and Soft-Switching DC-DC Converters," in Proc. 2014 IEEE Applied Power Electronics Conf., pp. 464-470.

- [8] Z. Zhang, K. D. T. Ngo, and J. L. Nilles, "A 30-W Flyback Converter Operating at 5MHz," in *Proc. 2014 IEEE Applied Power Electronics Conf.*, pp. 1415-1421.

- [9] J. Delaine, P. O. Jeannin, D. Frey, and K. Guepratte, "Improvement of GaN Transistors Working Conditions to Increase Efficiency of A 100W DC-DC Converter," in *Proc. 2013 IEEE Applied Power Electronics Conf.*, pp. 656-663.

- [10] W. Zhang, Y. Long, Y. Cui, F. Wang, L. M. Tolbert, B. J. Blalock, S. Henning, J. Moses, and R. Dean, "Impact of Planner Transformer Winding Capacitance on Si-based and GaN-based LLC Resonant Converter," in *Proc. 2013 IEEE Applied Power Electronics Conf.*, pp. 1668-1674.

- [11] J. Delaine, P. O. Jeannin, D. Frey, and K. Guepratte, "High Frequency DC-DC Converter Using GaN Device," in *Proc. 2012 IEEE Applied Power Electronics Conf.*, pp. 1754-1761.

- [12] S. Jiang, W. Zhang, B. Liu, and F. Wang, "Automatic Resonant Frequency Tracking in Unregulated LLC Resonant Converters Based on Total Resonant Current Harmonic Calculation," in *Proc. 2013 IEEE Energy Conversion Congress and Exposition Conf.*, pp. 4193-4198.

- [13] W. Zhang, Y. Long, Z. Zhang, F. Wang, L. M. Tolbert, B. J. Blalock, S. Henning, C. Wilson, and R. Dean, "Evaluation and Comparison of Silicon and Gallium Nitride Power Transistors in LLC Resonant Converter," in *Proc. 2012 IEEE Energy Conversion Congress and Exposition Conf.*, pp. 1362-1366.

- [14] D. Reusch and F. C. Lee, "High Frequency Isolated Bus Converter with Gallium Nitride Transistors and Integrated Transformer," in *Proc.* 2012 IEEE Energy Conversion Congress and Exposition Conf., pp. 3895-3902.

- [15] S. Miyawaki, J. Itoh, and K. Iwaya, "Optimization Design of an Isolated DC/DC Converter Using Series Compensation on the Secondary Side," in *Proc. 2010 IEEE Energy Conversion Congress* and *Exposition Conf.*, pp. 1428-1435.

- [16] D. Reusch and F. C. Lee, "High Frequency Bus Converter with Integrated Matrix Transformers for CPU and Telecommunication Applications," in *Proc. 2010 IEEE Energy Conversion Congress and Exposition Conf.*, pp. 2446-2450.

- [17] J. Wang, X. Yang, H. Niu, and Z. Wang, "PCB Integrated Transformer Composed with Ferrite Mosaics for LLC Resonant Converter," in *Proc.* 2009 IEEE Energy Conversion Congress and Exposition Conf., pp. 1032-1038.

- [18] Q. Li, M. Lim, J. Sun, A. Ball, Y. Ying, F. C. Lee, and K. D. T. Ngo, "Technology Road Map for High Frequency Integrated DC-DC Converter," in *Proc. 2010 IEEE Applied Power Electronics Conf.*, pp. 533-539.

- [19] (2014, Nov.). EPC2001 Enhancement Mode Power Transistor, Efficient Power Conversion, El Segundo, CA. [Online]. Available: http://epc-co.com/epc/documents/datasheets/EPC2001\_datasheet.pdf

- [20] J. Strydom, M. D. Rooij, and A. Lidow. (2012, Sep.). Gallium N itride Transistor Packaging Advances and Thermal Modeling. Effi cient Power Conversion Corp., El Segundo, CA. [Online]. Availa ble: http://epc-co.com/epc/documents/product-training/Gallium%20Ni tride%20Transistor%20Packaging%20Advances.pdf

- [21] Y. Xi, M. Chen, K. Nielson, and R. Bell, "Optimization of the Drive Circuit for Enhancement Mode Power GaN FETs in DC-DC Converters," in *Proc. 2012 IEEE Applied Power Electronics Conf.*, pp. 2467-2471.

- [22] S. Yang, M. Shoyama, and S. Abe, "Design of Low-Profile LLC Resonant Converter for Low Transformer Loss," in *Proc. 2010 IEEE Region 10 Conf.*, pp. 1301-1306.

- [23] B. Lu, W. Liu, Y. Liang, F. C. Lee, and J. D. Van Wyk, "Optimal Design Methodology for LLC Resonant Converter," in *Proc. 2006 IEEE Applied Power Electronics Conf.*, pp. 533-538.

- [24] T. Zaitsu, T. Ninomiya, M. Shoyama, and H. Tanaka, "PWM-Controlled Current-Mode Resonant Converter Using an Active-Clamp Technique," in *Proc. 1996 IEEE Power Electronics Specialists Conf.*, pp. 89-93.

- [25] W. J. Lee, S. W. Choi, C. E. Kim, and G. W. Moon, "A New PWM-Controlled Quasi-Resonant Converter for a High Efficiency PDP Sustaining Power Module," *IEEE Trans. Power Electron.*, vol. 23, pp. 1782-1790, Jul. 2008.

- [26] X. Xu, A. M. Khambadkone, T. M. Leong, and R. Oruganti, "A 1-MHz Zero-Voltage-Switching Asymmetrical Half-Bridge DC/DC Converter: Analysis and Design," *IEEE Trans. Power Electron.*, vol. 21, pp. 105-113, Jan. 2006.

Akinori Hariya (S'13) was born in Nagasaki, Japan, in 1989. He received the B.S. degree in electrical engineering from Nagasaki University, Japan, in 2012. Since 2012, he belongs to Graduate school of Engineering, Nagasaki University. He is currently working toward the Ph.D. degree. He received Excellent Student Award of Kyushu Section, IEICE in 2012.

Ken Matsuura was born in Saitama Prefecture, Japan, in 1975. He received the B.S. and M.S. degrees in electrical engineering from The University of Tokyo, Japan, in 1998 and 2000, respectively. Since 2000, he has joined TDK Corporation. He is currently an engineer of Energy Devices Development Center Technology HQ. His main job is to develop the switched-mode power supply, especially DC-DC converters.

**Hiroshige Yanagi** was born in Nagasaki Prefecture, Japan, in 1985. He received the B.S. and M.S. degrees in electrical engineering from Nagasaki University, Japan, in 2007 and 2009, respectively. Since 2009, he has joined TDK-Lambda Corporation. His main job is to design the switched-mode power supply, especially DC-DC converters and PFC converters.

Satoshi Tomioka was born in Niigata Prefecture, Japan, in 1961. He received the B.S. degree in electrical engineering from Tokyo Denki University, Japan, in 1984, and the Ph. D. degree in electrical engineering from Kyushu University, Japan, in 2011. Since 1984, he has joined TDK-Lambda Corporation (formerly NEMIC-LAMBDA K.K.). He is currently a Senior manager of technology development department & power module development R&D division. His main

job is research on switched-mode power supply, especially on DC-DC converters and PFC converters.

Yoichi Ishizuka (M'94) received the B.S., M.S. degrees from Kagoshima University, Kagoshima, Japan in 1994, and the Ph.D. degree from Kumamoto University, Kumamoto, Japan in 1996. In 1996, he joined the department of electric and electronics of engineering, Faculty of Engineering, Nagasaki University, Nagasaki, Japan as research assistant. Since 2008, he has been an associate professor of the same department. His research activities include switched-mode power supply stroller for SMPS.

(SMPS), adaptive controller for SMPS and integrated analog power circuits.

Tamotsu Ninomiya (M'89-SM'98-F'01) received the B.E., M.E., and Dr.Eng. degrees in electronics from Kyushu University, Fukuoka, Japan, in 1967, 1969, and 1981, respectively. Since 1969 he had been associated with the Department of Electronics, Kyushu University, and since 1988 he had been Professor. In March 2008, he retired from Kyushu University, and moved to Nagasaki University, Japan as Professor of TDK endowed chair, and retired in 2013. He now serves as Visiting Research

Professor at Asian Growth Research Institute in Kitakyushu city, Japan. He has been a specialist in the field of power electronics, including the analysis of switching power converters and their electromagnetic interference problems. He has published more than four hundred technical papers. He was Program Vice-Chairman for 1988 PESC, and General Chairman for 1998 PESC. For Japanese Institutes, he was awarded as IEICE Fellow in 2004, and as IEEJ Fellow in 2010.